一、NANDFlash

NAND Flash全名为Flash Memory,属于非易失性存储设备(Non-volatile Memory Device),基于浮栅(Floating Gate)晶体管设计,通过浮栅来锁存电荷,由于浮栅是电隔离的,所以即使在去除电压之后,到达栅极的电子也会被捕获。这就是闪存非易失性的原理所在。数据存储在这类设备中,即使断电也不会丢失。

根据不同的纳米技术,NAND Flash已经历了从SLC向MLC,再向TLC的过渡,正在向QLC迈进。NAND Flash凭借容量大、写入速度快等特点,广泛应用于eMMC/eMCP,U盘,SSD、汽车、物联网等领域。

SLC(英文全称(Single-Level Cell——SLC)即单层式储存

SLC技术特点是在浮置闸极与源极之中的氧化薄膜更薄,在写入数据时通过对浮置闸极的电荷加电压,然后透过源极,即可将所储存的电荷消除,通过这样的方式,便可储存1个信息单元,即1bit/cell,速度快寿命最长,价格贵(约MLC 3倍以上的价格),约10万次擦写寿命。

MLC(英文全称Multi-Level Cell——MLC)即多层式储存

英特尔(Intel)在1997年9月最先开发成功MLC,其作用是将两个单位的信息存入一个Floating Gate(闪存存储单元中存放电荷的部分),然后利用不同电位(Level)的电荷,通过内存储存的电压控制精准读写。

即2bit/cell,速度一般寿命一般,价格一般emmc,约3000—1万次擦写寿命。MLC通过使用大量的电压等级,每个单元储存两位数据,数据密度比较大,可以一次储存4个以上的值,因此,MLC架构可以有比较好的储存密度。

TLC(英文全称Trinary-Level Cell)即三层式储存

TLC即3bit per cell,每个单元可以存放比MLC多1/2的数据,共八个充电值,即3bit/cell,也有Flash厂家叫8LC,所需访问时间更长,因此传输速度更慢。

TLC优势价格便宜,每百万字节生产成本是最低的,价格便宜,但是寿命短,只有约1000次擦写寿命。

QLC(英文全称Quadruple-Level Cell)四层存储单元

全称是Quad-Level Cell,四层式存储单元,即4bits/cell。QLC闪存颗粒拥有比TLC更高的存储密度,同时成本上相比TLC更低,优势就是可以将容量做的更大,成本压缩得更低,劣势就是寿命更短,理论擦写次数仅150次。

(NAND Flash 四种类型 仅供参考)

PS:每Cell单元存储数据越多,单位面积容量就越高,但同时导致不同电压状态越多,越难控制,所以导致颗粒稳定性越差,寿命低,各有利弊。

(NAND Flash 读写寿命 仅供参考)

不难看出,四种类型的NAND闪存颗粒性能各有不同。SLC单位容量的成本相对于其他类型NAND闪存颗粒成本更高,但其数据保留时间更长、读取速度更快;QLC拥有更大的容量和更低的成本,但由于其可靠性低、寿命短等缺点,仍有待后续发展。

从生产成本、读写速度和使用寿命三方面来看,四类的排序都是:

SLC>MLC>TLC>QLC;

目前主流的解决方案为MLC与TLC。SLC主要针对军工,企业级应用,有着高速写入,低出错率,长耐久度特性。MLC主要针对消费级应用,容量高于SLC 2倍,低成本,适合USB闪盘,手机,数码相机等储存卡,如今也被大量用于消费级固态硬盘上。

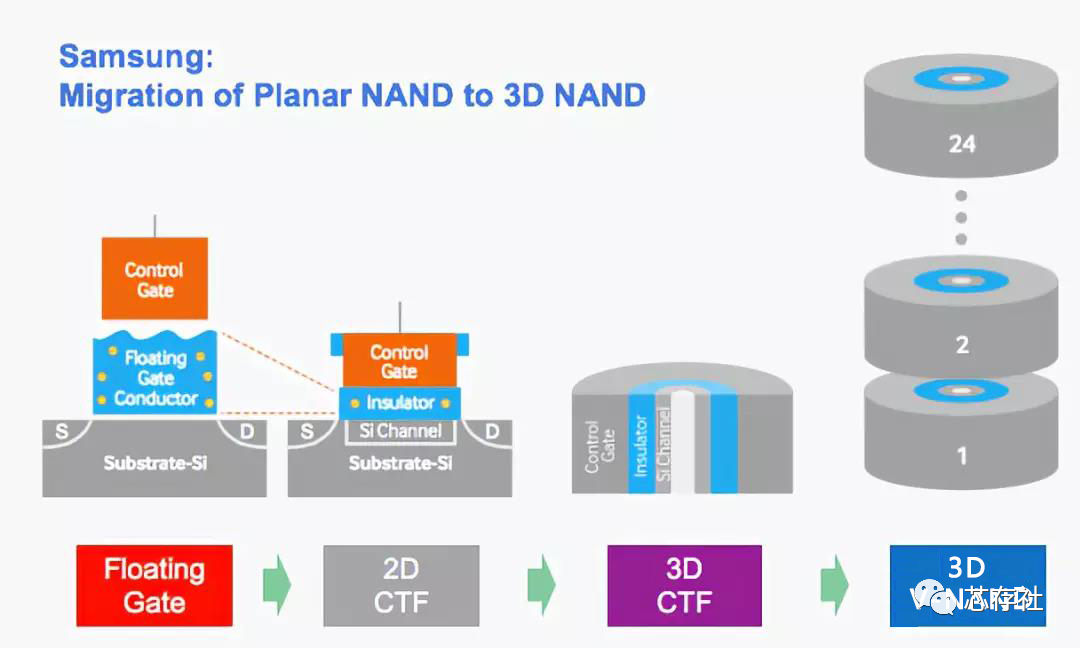

而NAND闪存根据对应不同的空间结构来看,这四类技术可又分为2D结构和3D结构两大类,浮栅晶体管是主要用于2D FLASH,3D flash主要采用的是CT晶体管,浮栅是半导体,CT是绝缘体,二者在本质和原理上就有区别。其区别在于:

2D结构NAND Flash

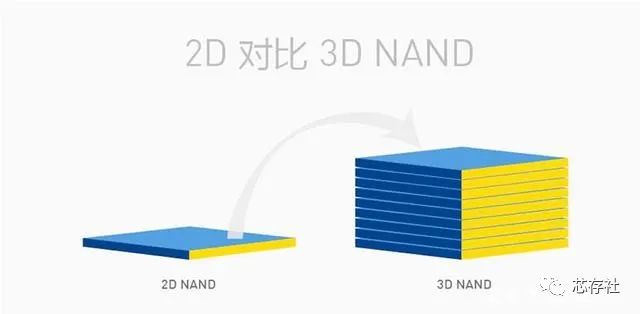

2D结构的存储单元仅布置在芯片的XY平面中,因而使用2D闪存技术在同一晶圆中实现更高密度的唯一方法就是缩小制程工艺节点。

其缺点是,对于较小的节点,NAND闪存中的错误更为频繁;另外,可以使用的最小制程工艺节点存在限制,存储密度不高。

3D结构NAND Flash

为了提高存储密度,制造商开发了3D NAND或V-NAND(垂直NAND)技术,该技术将Z平面中的存储单元堆叠在同一晶圆上。

在3D NAND闪存中,存储器单元作为垂直串连接而不是2D NAND中的水平串,以这种方式构建有助于为相同的芯片区域实现高位密度。第一批3D Flash产品有24层。

(2D NAND vs 3D NAND )

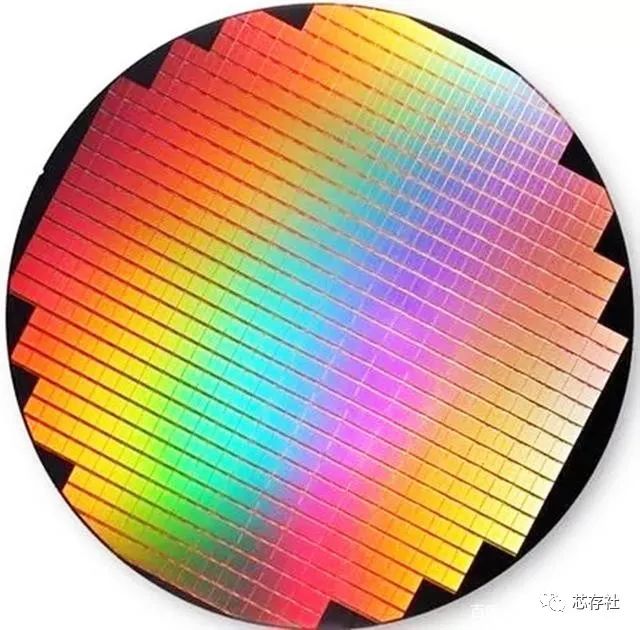

Nand Flash的加工过程

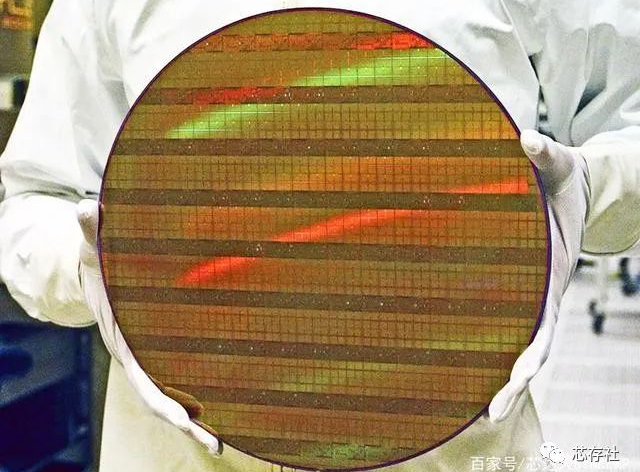

NAND Flash是从原始的硅材料加工出来的,硅材料被加工成晶圆(Wafer),一般分为6英寸、8英寸、12英寸规格不等,晶片就是基于这个wafer上生产出来的,一片晶圆可以切割出多少晶片是根据die的大小和wafer的大小以及良率来决定的,通常情况下,一片晶圆上可以做出几百颗NAND FLASH芯片。

芯片未封装前的晶粒成为Die,它是从Wafer上用激光切割而成的小片,每个Die就是一个独立的功能芯片,它由无数个晶体管电路组成,但最终可被作为一个单位封装起来成为闪存颗粒芯片。

晶片在光刻了电路后,称之为wafer

一片载有NAND Flash晶圆的wafer,wafer首先经过切割,然后测试,测试通过后,再进行切割、封装,封装完成后会再次进行一道检测。将完好的、稳定的、足容量的die取下,封装形成日常所见的Nand 。

在wafer上剩余的emmc,要么就是不稳定、要么就是部分损坏所以不足容量,或者是完全损坏。原厂考虑到质量保证,会将这种die宣布死亡,严格定义为废品全部报废处理。

合格的Flash Die原厂封装工厂会根据需要封装成eMMC、TSOP、BGA、LGA等产品,但封装的时候也有不良,或者性能不达标,这些Flash颗粒会再次被过滤掉,通过严格的测试确保产品的品质。

Wafer在切割前需要进行Wafer test

闪存颗粒制造厂商主要以三星(Samsung)、SK海力士(Hynix)、美光(Micron)、铠侠(原Toshiba)、Intel、闪迪(Sandisk)等为代表的几大厂商。

在国外NAND Flash主导市场的现状下,中国NAND Flash厂商长江存储(YMTC)异军突起在市场中占据一席之地,其推出的128层3D NAND在2020年第1季将128层3D NAND样品送交存储控制器厂商,目标第3季进入投片、量产,拟用于UFS、SSD等各类终端产品,并同时出货给模块厂,包含TLC以及QLC产品,以扩大客户基础。

NAND Flash的应用及发展趋势

NAND Flash作为一种比较实用的固态硬盘存储介质,有自己的一些物理特性。NAND Flash的寿命不等于SSD的寿命,SSD盘可以通过多种技术手段从整体上提升SSD的寿命,通过不同的技术手段,SSD盘的寿命可以比NAND Flash寿命提升20%~2000%不等。

反过来讲SSD的寿命不等于NAND Flash的寿命,NAND Flash的寿命主要通过P/E cycle来表征,SSD由多个Flash颗粒组成,通过盘片算法,可有效发挥颗粒寿命。

基于NAND Flash的原理和制造工艺,所有主要的闪存制造商都积极致力于开发不同的方法,以降低每比特闪存的成本,同时正在积极研究增加3D NAND Flash中垂直层的数量。

随着3D NAND技术的快速发展,QLC技术不断成熟,QLC产品也已开始陆续出现,可以预见QLC将会取代TLC,犹如TLC取代MLC一样。而且,随着3D NAND单die容量不断翻倍增长,这也将推动消费类SSD向4TB迈进,企业级SSD向8TB升级,QLC SSD将完成TLC SSD未完成的任务,逐渐取代HDD,这些都逐步的影响着NAND Flash市场。

研究统计范围包括8 Gbit、4Gbit、2Gbit以及其他小于16Gbit的SLC NAND闪存,产品应用于消费电子产品、物联网、汽车、工业、通信和其他相关行业。

国际原厂引领3D NAND 技术发展,在 NAND Flash 市场中,三星、铠侠(东芝)存储、美光、SK 海力士、闪迪、英特尔这六家原厂长期垄断着全球 99%以上的份额。

此外,国际原厂持续引领着3D NAND技术研发,形成了较为厚实的技术壁垒。但各原厂在设计方案上 的差别将会对其产出产生形成一定影响。三星、SK海力士、铠侠、闪迪已经相继发布最新100+层3D NAND产品。

当前阶段,NAND Flash 市场的发展主要受到智能手机和平板电脑需求的驱动。相对于机械硬盘等传统存储介质,采用NAND Flash 芯片的SD 卡、固态硬盘等存储装置没有机械结构,无噪音、寿命长、功耗低、可靠性高、体积小、读写速度快、工作温度范围广,是未来大容量存储的发展方向。随着大数据时代的到来,NAND Flash 芯片将在未来得到巨大发展。

二、eMMC、UFS

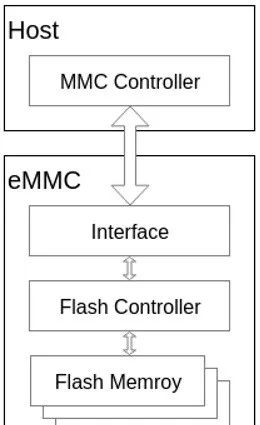

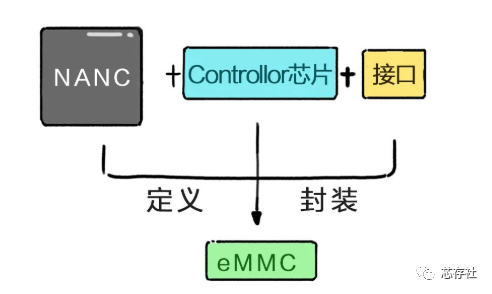

eMMC ( Embedded Multi Media Card) 采用统一的MMC标准接口, 把高密度NAND Flash以及MMC Controller封装在一颗BGA芯片中。针对Flash的特性,产品内部已经包含了Flash管理技术,包括错误探测和纠正,flash平均擦写,坏块管理,掉电保护等技术。用户无需担心产品内部flash晶圆制程和工艺的变化。同时eMMC单颗芯片为主板内部节省更多的空间。

简单地说,eMMC=Nand Flash+控制器+标准封装

eMMC的整体架构如下图片所示:

eMMC 则在其内部集成了 Flash Controller,用于完成擦写均衡、坏块理、ECC校验等功能,让 Host 端专注于上层业务,省去对 NAND Flash 进行特殊的处理。

eMMC具有以下优势:

1.简化类手机产品存储器的设计。

2.更新速度快。

3.加速产品研发速度。

eMMC标准

JEDD-2011年6月发布的JESD84-A441:Embedded MultiMediaCard(e•MMC)产品标准v4.5中定义的v4.5。JEDEC还发布了JESD84-B45:嵌入式多媒体卡e•MMC),2011年6月eMMC v4.5的电气标准(版本4.5设备)。2015年2月JEDEC发布eMMC标准 5.1版。

大多数主流中端手机采用的都是eMMC5.1的闪存,其理论带宽为600M/s。顺序读取速度为250M/s,顺序写入速度为125M/s。

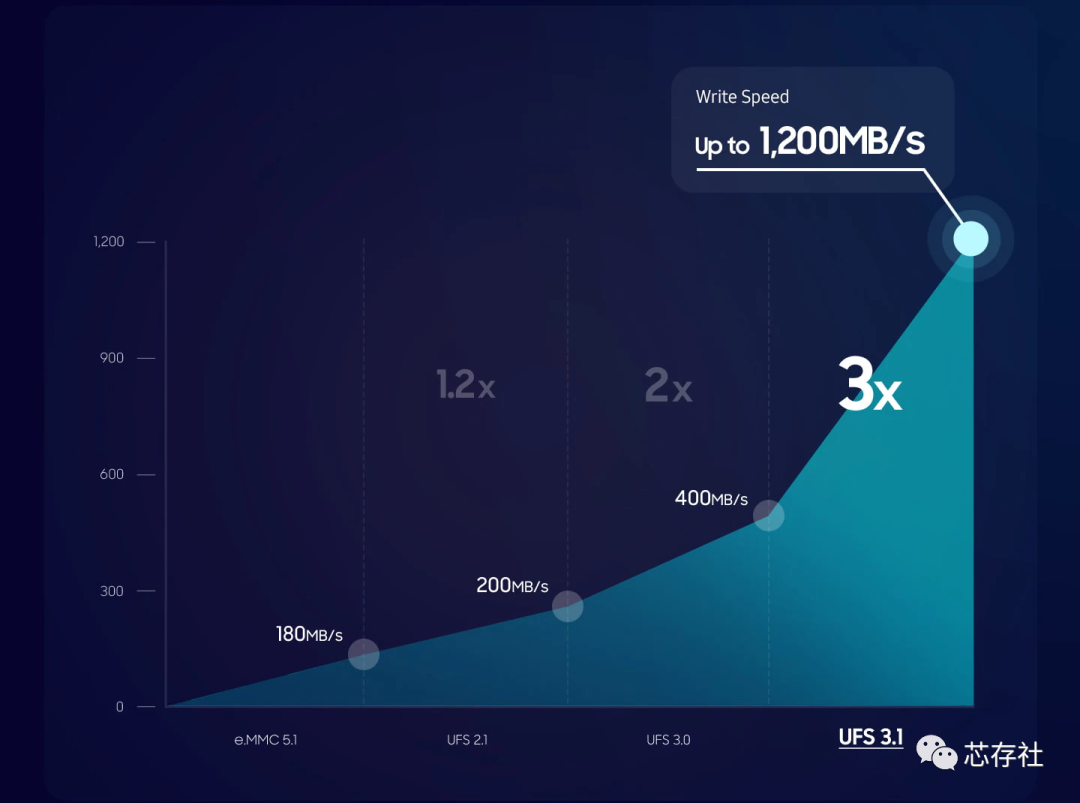

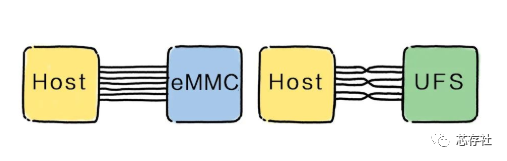

新一代UFS

UFS:Univeral Flash Storage,我们可以将它视为eMMC的进阶版,是由多个闪存芯片、主控、缓存组成的阵列式存储模块。UFS弥补了eMMC仅支持半双工运行(读写必须分开执行)的缺陷,可以实现全双工运行,所以性能得以翻番。

UFS早前被细分为UFS 2.0和UFS 2.1,它们在读写速度上的强制标准都为HS-G2(High speed GEAR2),可选HS-G3标准。而两套标准又都能运行在1Lane(单通道)或2Lane(双通道)模式上,一款手机能取得多少读写速度,就取决于UFS闪存标准和通道数,以及处理器对UFS闪存的总线接口支持情况。

UFS 3.0引入了HS-G4规范,单通道带宽提升到11.6Gbps,是HS-G3(UFS 2.1)性能的2倍。而由于UFS支持双通道双向读写,所以UFS 3.0的接口带宽最高可达23.2Gbps,也就是2.9GB/s。此外,UFS 3.0支持的分区增多(UFS 2.1是8个),纠错性能提升且支持最新的NAND Flash闪存介质。

为了满足 5G 设备的需求,UFS 3.1 的写入速度是上一代通用闪存存储的 3 倍。此驱动器的 1,200 百万字节/秒 (MB/s) 速度可增强高性能,有助于防止下载文件时缓冲,从而让您在连接频繁的世界中享受 5G 的低延迟连接性。

写入速度高达 1,200MB/s(写入速度可能因容量而异:128 千兆字节 (GB) 高达 850MB/s,256GB 和 512GB 高达 1,200MB/s)。

娜娜项目网每日更新创业和副业项目

网址:nanaxm.cn 点击前往娜娜项目网

站 长 微 信: nanadh666

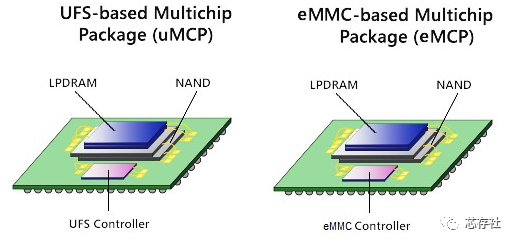

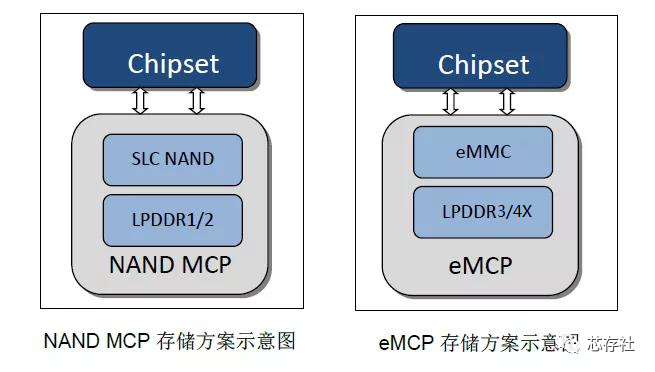

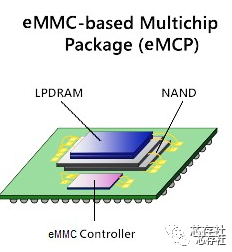

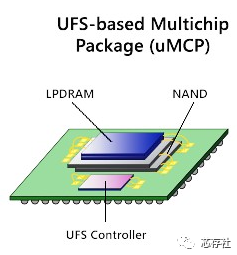

三、eMCP 与uMCP

eMCP是结合eMMC和LPDDR封装而成的智慧型手机记忆体标准,与传统的MCP相较之下,eMCP因为有内建的NAND Flash控制晶片,可以减少主晶片运算的负担,并且管理更大容量的快闪记忆体。以外型设计来看,不论是eMCP或是eMMC内嵌式记忆体设计概念,都是为了让智慧型手机的外型厚度更薄,更省空间。uMCP是结合了UFS和LPDDR封装而成的智慧型手机记忆体标准,与eMCP相比,国产的uMCP在性能上更为突出,提供了更高的性能和功率节省。

由于2016年NAND Flash市场严重缺货,导致eMMC和UFS价格水涨船高,其中eMMC价格最高累计涨幅超过60%,同时也拉大了eMMC与UFS之间的价差,考虑到成本的因素,大部分的中、低端手机依然以国产的eMMC、eMCP为主流存储方案,发展到现在UFS2.1依旧用在中高端手机上。

eMMC是将NAND Flash芯片和控制芯片都封装在一起,eMCP则是eMMC和LPDDR封装在一起。对于手机厂商而言,在存储产业陷入缺货潮的关键时期,既要保证手机出货所需的Mobile DRAM,又要保证eMMC货源,库存把控的难度相当大,eMCP自然成为大部分中低端手机首选方案。

早期的智能型手机,存储主流方案是NAND MCP,将SLC NAND Flash与低功耗DRAM封装在一起,具有生产成本低等优势。随着智能型手机对存储容量和性能更高的要求,特别是随着Android操作系统的广泛流行,以及手机厂商预装大量程序及软件,对大容量需求日益增加。

与传统的MCP相比,eMCP不仅可以提高存储容量,满足手机对大容量的要求,而且内嵌的控制芯片可以减少主CPU运算的负担,从而简化和更好的管理大容量的NAND Flash芯片,并节省手机主板的空间。

eMCP深受低端客户青睐,且仍在中低端手机中广泛应用,主要原因是eMCP具有高集成度的优势,包含eMMC和低功耗DRAM两颗芯片,对于终端厂商而言可以简化手机PCB板的电路设计,缩短出货周期。

其次,eMCP是将eMMC和低功耗DRAM进行封装,这样相较于eMMC和移动DRAM分开采购的价格要低,对于中低端手机而言有利于降低成本,尤其是在前2年NAND Flash和DRAM涨价的时期,更有利交易和议价。

uMCP是顺应UFS发展的趋势,满足5G手机需求

高端智能型手机基于对性能的高要求,CPU处理器需要与DRAM高频通讯,所以高端旗舰手机客户更青睐采用CPU和LPDDR进行POP封装,分立式eMMC或UFS的存储方案,这样线路设计简单,可以减轻工程师设计PCB的难度,减少CPU与DRAM通讯信号的干扰,提高终端产品性能,随之生产难度增大,生产成本也会增加。

5G手机的发展将从高端机向低端机不断渗透,实现全面普及,同样是对大容量高性能提出更高的要求,uMCP是顺应eMMC向UFS发展的趋势。

uMCP结合LPDDR和UFS,不仅具有高性能和大容量,同时比PoP +分立式eMMC或UFS的解决方案占用的空间减少了40%,减少存储芯片占用并实现了更灵活的系统设计,并实现智能手机设计的高密度、低功耗存储解决方案。

综上所述简单总结一下:

eMMC=Nand Flash+控制器+标准封装

UFS=eMMC的进阶版

eMCP=eMMC+LPDDR+标准封装

uMCP=UFS+LPDDR

四、DDR、LPDDR

DDR全称Double Data Rate双倍速率同步动态随机存储器,严格的来讲,DDR应该叫DDR SDRAM。虽然美国固态技术协会2018年宣布正式发布DDR5标准,但实际上最终的规范要到2020年才能完成,其目标是将内存带宽在DDR4基础上翻倍,速率3200MT/s起,最高可达6400MT/s,电压则从1.2V降至1.1V,功耗减少30%。

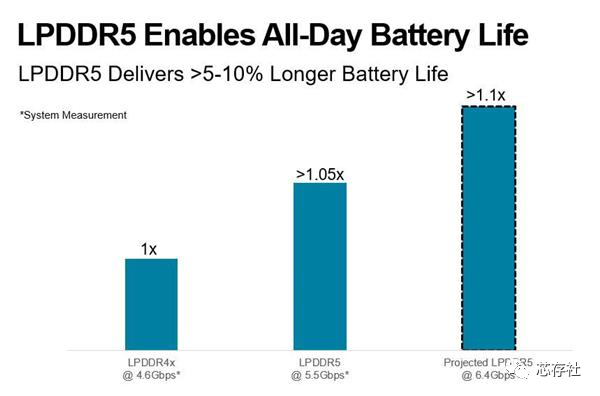

LPDDR是在DDR的基础上多了LP(Low Power)前缀,全称是Low Power Double Data Rate SDRAM,简称“低功耗内存”是DDR的一种,以低功耗和小体积著称。目前最新的标准LPDDR5被称为5G时代的标配,但目前市场上的主流依然是LPDDR3/4X。

DDR和LPDDR有什么不同呢?

应用领域不同。DDR因其更高的数据速率、更低的能耗和更高的密度广泛应用于平板电脑、机顶盒、汽车电子、数字电视等各种智能产品中,尤其是在疫情期间,由于在家办公、网课和娱乐的增加,平板电脑、智能盒子的需求也逐步攀升,这对DDR3、DDR4的存储性能要求更高、更稳定。

而LPDDR拥有比同代DDR内存更低的功耗和个小的体积,该类型芯片主要应用于移动式电子产品等低功耗设备上。

LPDDR和DDR之间的关系非常密切,简单来说,LPDDR就是在DDR的基础上面演化而来的,LPDDR2实在DDR2的基础上演化而来的,LPDDR3则实在DDR3的基础上面演化而来的,以此类推。但是从第四代开始,两者之间有了差别或者说走上了不同的发展,主要因为DDR内存主要是通过提高核心频率从而提升性能,而LPDDR则是通过提高Prefetch预读取位数而提高使用体验。同时在商用方面,LPDDR4首次先于DDR4登陆消费者市场。

以目前使用量最高的DDR4和LPDDR4来举例,LPDDR4是通过两个16位通道组成的32位总线,而DDR4却具备原生64位通道,LPDDR4的Prefetch预读取位位16位,而DDR4为8位,所以在实际运算的过程中,DDR4的性能利用率会更高,但LPDDR却可以用耕地的功耗来获得更高的理论性能。

所以,也不存在LPDDR5的技术比DDR5更先进,性能跟高这一说法,并且如果论性能的话,DDR的性能始终是高于同代的LPDDR内存的性能的。

桌面级的DDR内存在技术升级方面要慢于移动端,LPDDR内存由于在便携设备的功耗占比比较高,况且同时还担负着显存这一身份的重任,技术的迭代对于手机性能和功耗有着巨大的影响,所以相比较于DDR内存,LPDDR内存更容易被用户感知。

因为和手机相比,电脑对功耗的要求没有那么高,也没有那么敏感,所以很多轻薄笔记本还在使用LPDDR3的内存,即使最新的英特尔处理器也只支持LPDDR4X内存,DDR5的正是规范标准今年才会完成制定,即使标准制定完成,今年也不会看到很多搭载DDR5内存的电脑。而LPDDR5则是今年绝大部分旗舰机型的标配,相比DDR5,LPDDR5会在很多手机上面看到。

而在性能方面,LPDDR和DDR各有千秋,比如LPDDR5目前在数据传输速率上,理论性能的确领先DDR4一个身位,但这并不代表LPDDR5一定比DDR4更强。

电子产品的进步总结下来一定是体积更小,性能更强,功耗更低。当然内存也不例外,无论是LPDDR内存还是DDR内存,或许有一天能通过极低的功耗,实现更高的性能。

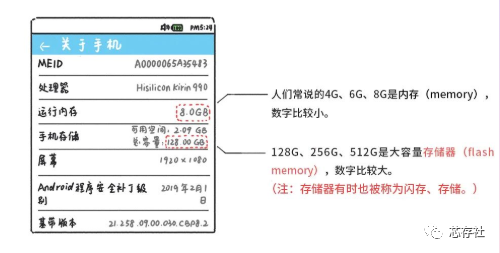

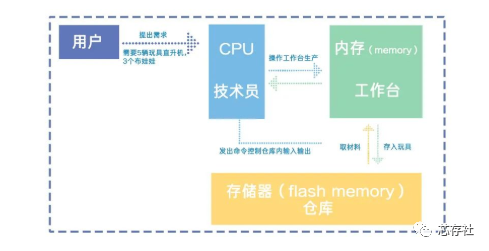

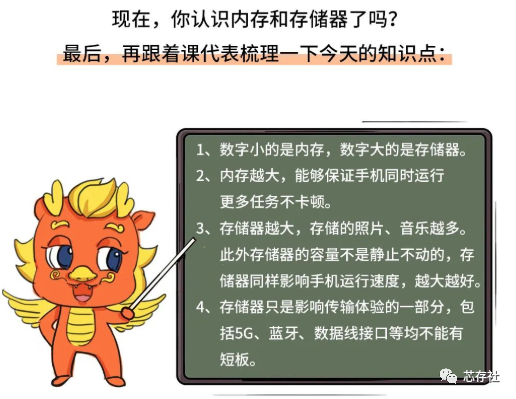

五、存储器和内存如何快速区分

以上如果觉得有用欢迎转发收藏,谢谢。

娜娜项目网每日更新创业和副业项目

网址:nanaxm.cn 点击前往娜娜项目网

站 长 微 信: nanadh666